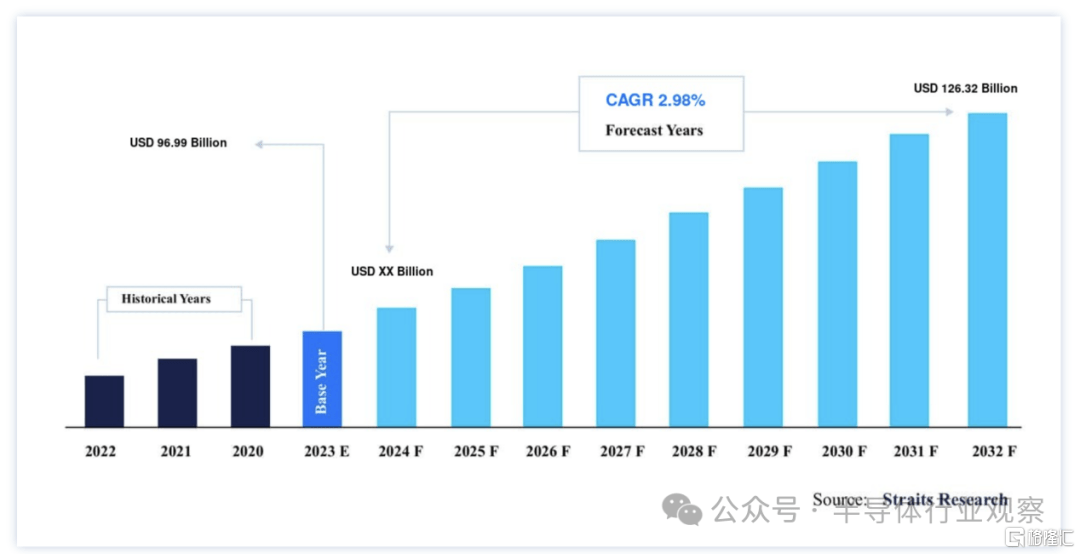

作爲半導體市場規模最大的細分產品之一,DRAM的影響力不言而喻。據straitsresearch的數據顯示,2022 年全球動態隨機存取存儲器 (DRAM) 市場規模爲 969.9 億美元。預計到2031 年將達到 1263.2 億美元,預測期內(2023-2031) 的復合年增長率爲 2.98%

在straitsresearch看來,DRAM之所以在未來能獲得高速發展,除了筆記本電腦/平板電腦、智能手機和數碼相機等消費電子產品銷量穩步發展以外,雲計算、人工智能、物聯網等大趨勢的不斷發展也是DRAM能夠長期看好的關鍵因素。

但如果細看終端需求,我們可以發現,人工智能推動下的HBM會是DRAM未來發展的重要動力來源。市場分析機構TrendForce 在五月曾表示,HBM 在 DRAM 總位容量中的份額預計將從 2023 年的 2% 上升到 2024 年的 5%,到 2025 年將超過 10%。如果按價值計算,預計從 2024 年开始 HBM 將佔 DRAM 總市場價值的 20% 以上,到 2025 年可能超過 30%。

但其實除了HBM以外,包括三星、SK海力士和美光在內的DRAM巨頭,正在各個方向發力,以求在DRAM未來不會錯失良機。

HBM,愈演愈烈

HBM已經成爲了全球關注點,在此前的文章《HBM 4,即將完成》中,我們已經披露了三大巨頭的下一階段的競賽。但其實在此之前,圍繞着HBM3e的爭奪還在如火如荼進行。

在今年 2 月,三星電子首次實現最大容量 36GB HBM3E 12 層高帶寬存儲器 (HBM),在半導體行業實現了重大飛躍。據業內人士 7 月 16 日透露,三星已於第二季度开始量產這款第五代 HBM 產品,目前正在向特定客戶供貨。

HBM3E 12 層採用硅通孔 (TSV) 技術將 DRAM 內存芯片堆疊多達 12 層,正在成爲今年下半年 AI 半導體市場的關鍵战場。這一發展加劇了內存公司之間的競爭,三星電子、SK 海力士和美光都在爭奪主導地位。

三星電子必須通過質量測試(Qual Test),才能在下半年向 NVIDIA 供應其 HBM3E 12 層產品。盡管成功實現量產,但未能通過質量測試可能會導致預生產產品積壓爲庫存。因此,三星正全力以赴滿足 NVIDIA 的標准。

SK Hynix 也參與了競爭,准備在第三季度量產其 HBM3E 12 層。雖然它目前向 NVIDIA 供應之前的 HBM3E 8 層,但它尚未收到 12 層版本的質量測試請求。SK Hynix 通過將量產時間表從明年提前到第三季度,正在加速其市場領先地位。

美光則是此次競爭中的一匹黑馬,計劃在下半年完成 HBM3E 12 層量產准備,並於明年向 NVIDIA 等大客戶供貨。由於目前尚未有一家內存公司決定向 NVIDIA 供應 HBM3E 12 層,因此美光很可能會同時考慮三家公司的報價,以滿足需求並確保有利的價格。

業界相關人士表示,“即使由於競爭加劇,HBM3E 12層的價格可能會略有下降,但下半年顯然是決定HBM市場格局的時候。”該人士補充道,“關鍵在於各家公司能將良品率提高多少。”

今年下半年對於確定 HBM 市場的未來格局至關重要。誰先向 NVIDIA 供應 HBM3E 12 層產品將決定 SK 海力士能否保持 HBM 領先地位,還是三星電子扭轉局勢。競爭非常激烈,賭注很高,因爲確保 HBM3E 12 層的領先地位可能會對每家公司的市場地位和財務狀況產生重大影響。

LPDDR,持續火熱

如韓媒Chosun所說,半導體行業曾經專注於速度和容量,現在正轉向功率效率。隨着人工智能學習和訓練變得越來越先進,處理海量數據所需的功率也大幅增加,導致开發低功耗芯片的競爭愈演愈烈。

人工智能芯片通常被稱爲“耗能大戶”,是耗電量大戶。英偉達即將推出的高性能人工智能芯片 B100 需要 1000 瓦的功率。之前的人工智能芯片型號 A100 和 H100 分別需要 400 瓦和 700 瓦,這表明性能越高,功耗也就越大。

三星電子和 SK 海力士是供應 AI 芯片所用內存芯片的領先芯片制造商,它們正在推出新的低功耗半導體解決方案。

低功耗芯片對於智能手機、平板電腦和筆記本電腦等設備至關重要,這些設備需要在不連接互聯網的情況下執行 AI 計算,同時節省電池壽命。“低功耗半導體可以延長移動設備的電池壽命,並減少服務器數據處理所需的能量,”一位半導體業內人士表示。“隨着電源變得越來越稀缺,低功耗半導體將變得更加重要。”

LPDDR,即低功耗雙倍數據速率內存,是低功耗芯片的前沿。與具有單個數據路徑的傳統 DRAM 不同,DDR 具有兩個路徑,從而可以更快地處理數據。LPDDR 還可以降低功耗,並且已經开發到第 7 代 (5X)。它們通常用於高性能智能手機和筆記本電腦。

三星電子和 SK 海力士都在加快 LPDDR 研發。今年 4 月,三星开發出 LPDDR5X(第 7 代),這是迄今爲止數據處理速度最快的低功耗 DRAM 芯片。該公司最近完成了速度驗證,據報道正在爲量產做准備。這款新產品的容量比上一代產品高出 30% 以上,同時功耗降低了 25%。該公司採用了根據性能和速度調整功率的新技術。

SK海力士去年年底首次將性能提升5倍的LPDDR5T DRAM商業化,該產品被中國智能手機制造商Vivo的旗艦機型採用,可在一秒鐘內處理15部全高清電影,同時顯著降低功耗。

最近,LPDDR 堆疊技術也得到了大力發展。與堆疊多個 DRAM 的 HBM(高帶寬內存)一樣,LPDDR 堆疊旨在提高容量和速度,同時最大限度地降低功耗。

與此同時,下一代的LPDDR6 標准也在同步推進中。

據今年三月的一個消息透露,國際半導體標准組織(JEDEC)在裏斯本的會議上就LPDDR6標准進行了廣泛的討論。消息顯示,新的 LPDDR6 RAM 可以實現高達 12,800 MT/s 的最大數據速率。

據預計,LPDDR6標准的制定將重點關注提高數據處理性能。這是因爲,隨着智能手機、筆記本電腦和平板電腦上進行大規模AI計算的設備端AI需求的快速增長,內存性能的重要性進一步得到強調。此外,據悉,用電標准也將提高。

消息人士更是指出:“技術开發和標准討論正在以最小化功耗的方式進行,功耗隨着數據處理的增加而增加。”

細分市場,各出奇招

在圍繞着標准市場發力以外,這些DRAM大廠也在盯住細分市場,各出奇招。

首先看三星方面,據了解,三星電子正在开發爲蘋果下一代 XR 設備供應 LLW DRAM 的技術。據業內人士透露,三星電子正在开發向蘋果供應LLW DRAM的產品。

LLW DRAM 是下一代 DRAM,與傳統移動產品 LPDDR 相比,新技術通過增加輸入/輸出 (I/O) 端子的數量來增加帶寬(發送和接收數據的路徑)。通過此,它具有 128GB/s 的高性能和低延遲特性。得益於此,它有望應用於端側AI行業,取代現有的LPDDR。

據說蘋果公司也對 LLW DRAM 非常感興趣。事實上,蘋果在去年 6 月推出其尖端 XR 設備“Vision Pro”時就採用了 SK Hynix 的 LLW DRAM。相關報道指出,爲了支持 R1 的高速處理,SK 海力士开發了定制的 1 千兆位 DRAM。據悉,新 DRAM 將輸入和輸出引腳數量增加了八倍,以最大限度地減少延遲。這種芯片也稱爲低延遲寬 IO。據專家介紹,新芯片似乎還採用了一種特殊的封裝方法——扇出型晶圓級封裝——作爲單個單元連接到 R1 芯片組。

如前所說,三星電子還被發現繼續开發向蘋果供應 LLW DRAM 的技術。

一位知情人士解釋說,“據了解,三星收到了蘋果公司在 2022 年供應 LLW DRAM 的提議”,並補充道,“我們目前正在將該產品商業化,包括小批量生產。”另一位官員表示,“三星電子正試圖在蘋果的LLW DRAM供應鏈中追趕SK海力士”,並補充道,“作爲一種特殊存儲器,它可以用於下一代Vision Pro等。”

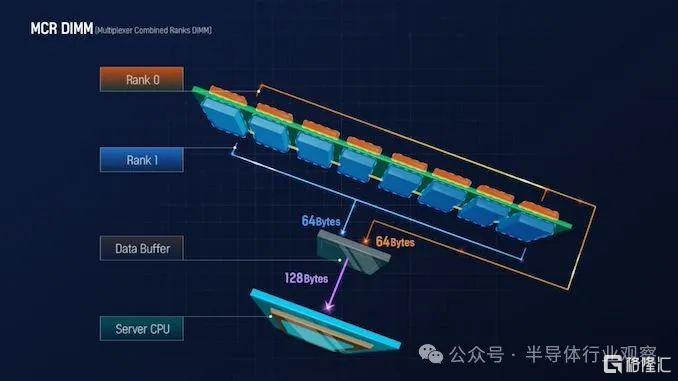

針對數據中心市場的DRAM,廠商們也紛紛亮劍。例如因應服務器和數據中心對帶寬的需求,DRAM大廠正在採取各種方法將DRAM速度提高到DDR 5的最高速度之外。在2022 年底,SK 海力士推出了用於特定英特爾服務器平台的 MCR-DIMM。該技術被稱爲多路復用器組合等級 (MCR) DIMM,允許高端服務器 DIMM 以最低 8 Gbps 的數據速率運行,與現有 DDR5 內存產品 (4.8 Gbps) 相比,帶寬提高了 80%。MCR DIMM 背後的技術很有趣,因爲它可以同時使用兩個ranks而不是一個,本質上是將兩組/等級的內存芯片組合起來,以使有效帶寬翻倍。

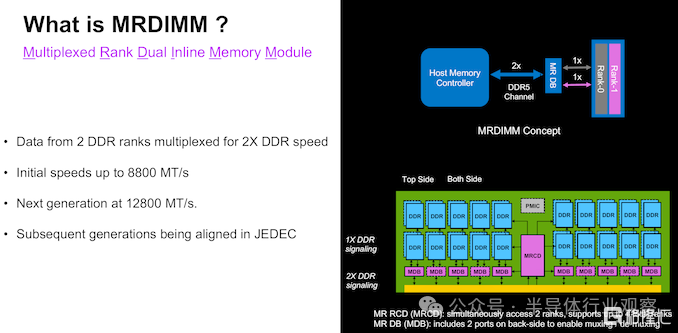

與此同時,標准制定機構 JEDEC 也以類似的方法制定了 MR-DIMM 的規範。它們都以現有的 DDR5 技術爲基礎,試圖結合多個等級來改善峰值帶寬和延遲。

MR-DIMM 標准在概念上很簡單,有多個以標准 DDR5 速度運行的內存模塊,前面有一個數據緩衝區。緩衝區在主機接口端以 2 倍的速度運行,從而允許傳輸速率翻倍。這個設計的挑战也是很顯而易見——在於能夠以更高的速度運行主機內存控制器中的邏輯並控制功耗/熱量。

JEDEC MR-DIMM 標准的第一版規定速度爲 8800 MT/s,下一代規定速度爲 12800 MT/s。JEDEC 還爲這項技術制定了明確的路线圖,使其與 DDR5 標准的改進保持同步。

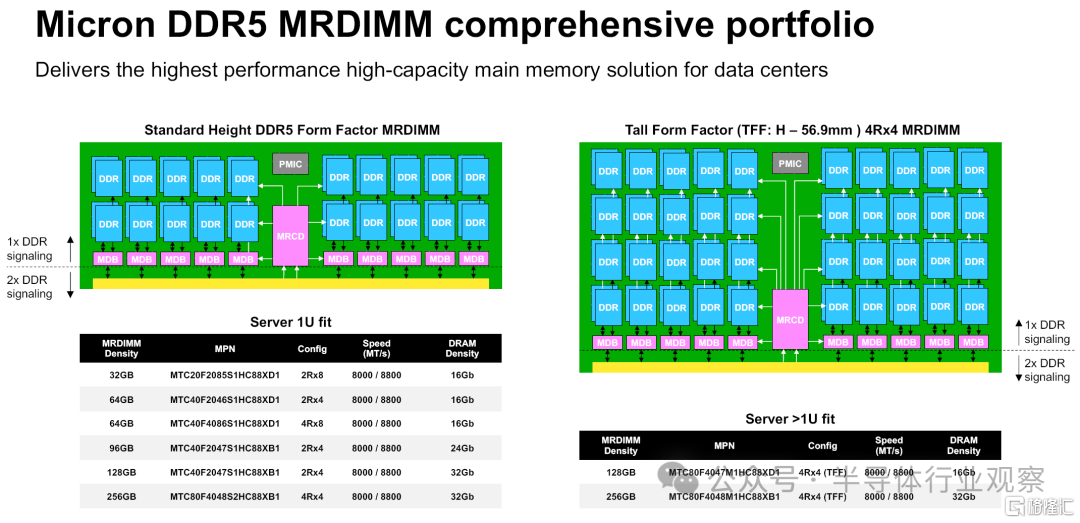

在過去幾個季度中,美光和英特爾一直密切合作,將前者的第一代 MR-DIMM 系列推向市場。

從 JEDEC 規範中可以看出,MR-DIMM 的優勢在於可以提高數據速率和系統帶寬,同時改善延遲。在容量方面,由於允許在模塊上增加列數,Micron 能夠提供 256 GB 的容量。必須注意的是,一些供應商也在使用 TSV(硅通孔)技術來增加標准 DDR5 速度下的每封裝容量,但這會增加額外的成本和復雜性,而 MR-DIMM 制造過程中基本上不存在這些成本和復雜性。

美光也不是第一個公开宣布 MR-DIMM 樣品的公司。三星上個月宣布了自己的產品线(基於 16Gb DRAM 芯片)。

三星表示,公司开發了多級緩衝雙列直插式內存模塊 (MRDIMM),無需增加服務器主板上的內存插槽即可提供更多內存和帶寬。該模塊通過組合兩個 DDR5 組件,使現有 DRAM 組件的帶寬翻倍,提供高達 8.8 Gb/s 的數據傳輸速度。預計 MRDIMM 將積極用於需要高性能計算 (HPC) 來處理數據並高速執行復雜計算的 AI 應用。三星強調,公司目前正在對 16Gb Mono MRDIMM 設備進行送樣,該設備具有增強的性能、容量和功耗。憑借這一創新的內存解決方案,三星正在推動人工智能 (AI)、機器學習 (ML) 和大型語言模型 (LLM) 處理的下一個前沿。

寫在最後

本文主要圍繞當前的一些熱點話題,分享三大內存企業各自的想法,以供各位參考。

展望未來,如Techinsights所說,DRAM 對於 DDR5、LPDDR5/5X、GDDR6/6X、HBM2E/HBM3/HBM3E 和低延遲 DRAM (LLDRAM) 等應用仍然至關重要。內存處理 (PIM) 和 Compute Express 鏈路近內存處理 (CXL-PNM) 等創新正在提高性能和效率。

Techinsights指出,三星和 SK 海力士已將 D1a 和 D1b 單元設計產品商業化,包括 DDR5、LPDDR4X、LPDDR5 和 LPDDR5X,具有最小的 12nm 級 DRAM 單元設計。兩家公司在採用 EUV 光刻技術方面都處於領先地位,而美光則繼續將基於 ArF 和 ArFi 的圖案化技術應用到其 1α 和 1β 代,並計劃在其 1γ 代中引入 EUV。三星在 D1a 和 D1b 代中將 EUV 光刻擴展到五個或更多掩模。SK 海力士遵循類似的 EUVL 策略,已將其用於 D1a 和 D1b 代,並計劃在未來幾代中增加 EUVL 步驟。

“明年初,各大廠商將推出量產的 D1c DRAM ,隨後在 2026 年或 2027 年推出最終的 10nm 級 DRAM 設備(D1d 或 D1δ 節點)。到 2030 年,DRAM 技術預計將縮小到個位數納米節點,包括 0a、0b、0c 或 0α、0β 和 0γ 代。三星正在开發 VS-CAT 和 VCT 3D DRAM,而 SK 海力士和美光則專注於垂直堆疊 DRAM。”Techinsights強調。

Techinsights認爲,DRAM 技術的未來前景光明,有望滿足高性能應用和新興技術日益增長的需求。

標題:DRAM,新競賽!

鄭重聲明:本文版權歸原作者所有,轉載文章僅為傳播信息之目的,不構成任何投資建議,如有侵權行為,請第一時間聯絡我們修改或刪除,多謝。